Broadcast quality and never-freeze design

- “Broadcast quality” brand we attained through a lot of development activities in collaboration with broadcast equipment manufacturers;

- Never-freeze design technology to prevent broadcast accidents; Structure to return to the initial state always at the boundary between frames or others

High speed communication technology at a level high enough to carry out a national project

- In the field of high speed communication, our technology is high enough not only to develop industrial-use routers but also to carry out the national project of OTN (Optical Transport Network) by us alone.

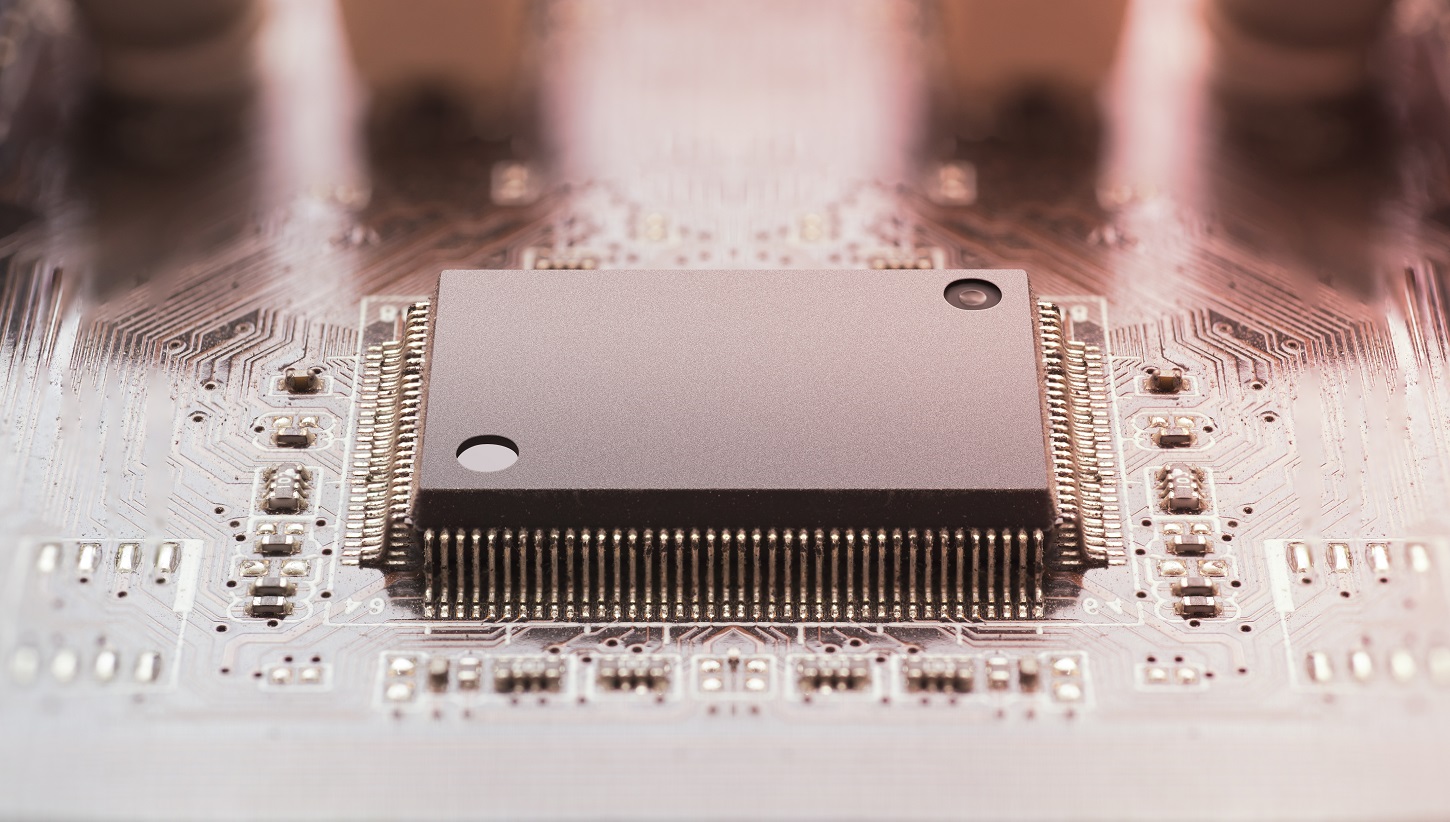

Record of zero-times remaking

- No remaking has been required in the past 20 or more ASIC development projects we undertook.

- In the field of FPGA development, we are using simulation techniques acquired through ASIC development and we are adopting the most up-to-date techniques such as the use of Lint and other tools.

Sticking to a beautiful RTL

- Unified description style to care about every single space

- Design style faithful to fundamentals like lining up TTL-ICs; “Simple is best.”

Training of backbone employees of a major semiconductor vendor

- Gave lectures in the RTL design and logic composition courses (for two major semiconductor vendors)